【第五届集创赛】倒计时10天!第五届集创赛喊你来报名!

由工业和信息化部人才交流中心主办的全国大学生集成电路创新创业大赛顺利走到第五个年头(简称集创赛),集成电路是信息技术产业的核心,是支撑经济社会发展的基础性和先导性产业,本着培养优秀的后备人才的原则,海云捷迅作为第五届集创赛执行承办方,举起科技创新大旗,投入到人才培养事业中来。

海云捷迅作为一家企业私有云和全架构智能计算服务商,拥有十余年开源云技术研发基础,在2018年与主流处理器芯片三大宗门之一的FPGA结缘,几年的时间将FPGA的硬件可编程性、灵活性特点与云计算业务相融合,推出一系列产品化解决方案,并重点进军教育行业,将实践经验与理论相结合,为在校高校师生提供教育解决方案,为FPGA产学研协同及生态建设提供支持。

集创赛作为全国高校学科竞赛榜集成电路领域唯一入榜赛事,也是行业最大规模赛事,每年都会吸引千余支队伍报名参赛,来自全国万余名高校学生同台竞技。本届大赛为本硕博不同阶段的参赛者量身打造的六大赛道,18个企业杯赛均为极具价值的工程实战项目。其中由海云捷迅作为企业代表参与赛题设置的海云捷迅杯在FPGA设计与应用赛道静待大家参与,其赛题为《基于FPGA C5Soc的MobileNetV1 SSD目标检测方案设计》,第五届集创赛海云捷迅杯官网已正式上线(点击进入官网报名页面)

海云捷迅杯赛事详情

第五届集创赛——海云捷迅杯

杯赛题目:基于FPGA C5Soc的MobileNetV1 SSD目标检测方案设计

参赛组别:B组

设计任务:

- 基于已训练好的SSD模型参数文件、基于已有的Intel FPGA工程网表文件、Linux-C5soc平台的Paddle-Paddle框架驱动为参考,优化或者重新设计加速器以及对应驱动,并部署SSD模型到FPGA进行推理。

- 对方案进行评估和实现

- 提出设计方案,提升性能并实现

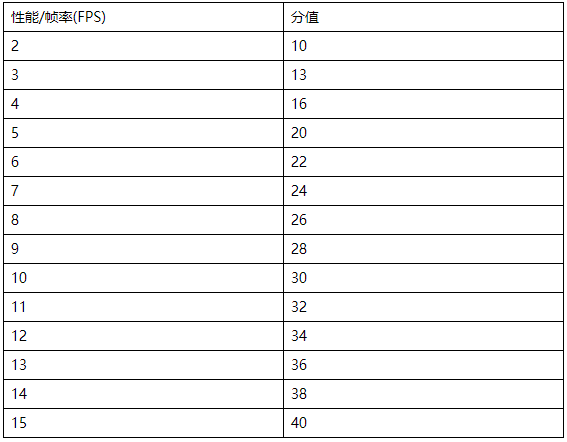

- 基础部分100,附加部分40分。最后总分按两部分相加得到。

备注:SSD模型参数文件、工程网表文件,包括整个工程结构顶层以及各模块连接关系,包括卷积、全连接等算子以及互联矩阵、调度模块等CNN加速器的完整工程。

设计指标:

- 模型部署完成,能正确识别图片数据,推理时间1s以内。

- 完成方案设计,完成方案设计文稿

附加题:

根据提供的网表和驱动文件,根据Demo工程重新设计加速器底层Verilog工程结构及相应驱动

提交内容:

- 汇报PPT:项目介绍、关键技术介绍、性能指标

- 详细设计方案:系统架构分析、关键技术分析、性能分析

- 驱动源码以及底层Verilog工程源码、仿真以及测试报告。

评分标准:

参考文献:

- 基于Paddle框架的手写体实验DEMO。包括驱动文件以及FPGA网表文件。

- 海云捷迅人工边缘智能实验平台使用手册。

- 飞桨官方网站https://www.paddlepaddle.org.cn/

- 《Cyclone V Hard Processor System Technical Reference Manual》

- 《AIGO_C5MB_V10 Schematic》

- 《Cyclone V SoC 开发板产品手册》

- MobileNetV1 SSD的模型参数文件

注意事项:

- 参加杯赛的作品,杯赛出题企业有权在同等条件下优先购买参加本企业杯赛及单项奖获奖团队作品的知识产权。

- 大赛组委会对参赛作品的提交材料拥有使用权和展示权。

赛事详情咨询:

联系人:李老师

座机号:(010)68208716

手机号:15201338583(微信同号)

“海云捷迅”杯赛题咨询:

联系人:黄老师

手机号:13452151971(微信同号)